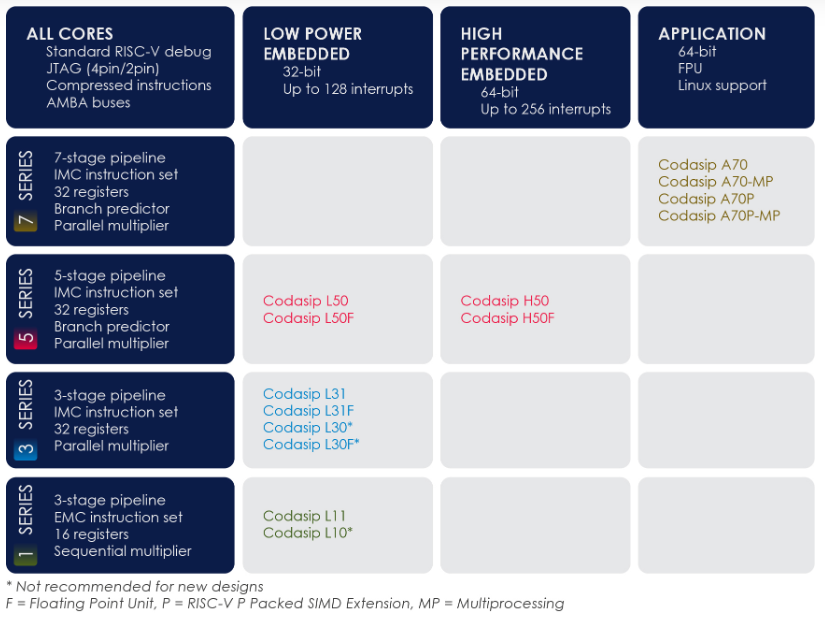

Codasip RISC-V processors are fully verified and ready for rapid deployment, or to be used as a quick-start base for customisation using Codasip Studio, an incredible tool for processor design automation, which we’ll talk about in just a moment. To begin, Codasip offers a range of off-the-shelf microarchitectural implementations of the RISC-V standard for virtually any application requirements. For the embedded domain, they provide processors with focus on two different primary needs: small and efficient Low Power Embedded cores (32-bit), and more powerful High Performance Embedded cores (64-bit). In addition to these, they offer Application cores able to run Linux with multiple series in each domain based on your required microarchitecture complexity.

But as good as they are, these off-the-shelf products are not what make Codasip one to write about. Because their cores are based on the open RISC-V architecture, where innovation is modular and flexible, allowing designers to create custom instructions to achieve their performance, power or area goals, this gives Codasip the ability to make all their RISC-V CPUs fully customisable and adaptable to the unique needs of YOUR project.

The image above shows Codasip’s range of basic RISC-V CPUs, but the real beauty of these products is that, using Codasip Studio, you can tweak these existing processor designs, or simply create brand-new processor cores. Codasip Studio covers every aspect of the design process and makes the path to your custom core supremely smooth, fast, and risk-free. Codasip also provides ample coding and SDK infrastructure to make sure your configurations work as intended and free of bugs.

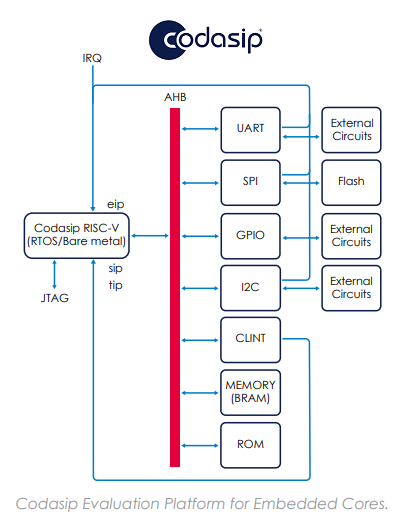

For an otherwise mind-blowing technology, as far as we’re concerned, Codasip have created an easy way to evaluate any of their RISC-V processors using two new FPGA evaluation platforms. Targeting popular Digilent boards, the platforms are supplied with everything you need to get started in a matter of minutes. These platforms, one for embedded and one for application cores, consist of your selected RISC-V processor with a subsystem containing peripherals and AMBA interconnect. A testbench layer includes a clock generator and block RAMs for internal memories and can use some of the FPGA peripherals such as flash memory. Additionally, users receive a Vivado project and bitstream files for their target FPGA board. The platforms include an SDK, software examples, and step-by-step documentation on how to use the peripherals.

If a custom RISC-V processor is just what you’re looking for, we suggest simply filling out an evaluation form and getting a chat going with Codasip. Hey! Mythic is even one of the case studies mentioned on their website, so you know this technology is serious business!

Keep designing!

(Images sourced from Codasip)