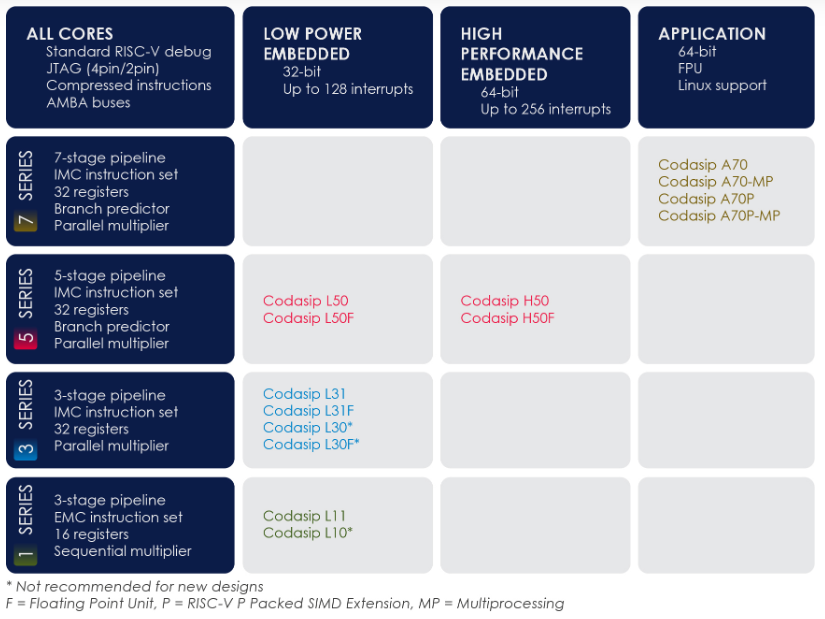

Codasip RISC-V processors are fully verified and ready for rapid deployment, or to be used as a quick-start base for full customisation using Codasip Studio, an incredible tool for processor design automation. Codasip offers a range of off-the-shelf microarchitectural implementations of the RISC-V standard for virtually any application requirements.

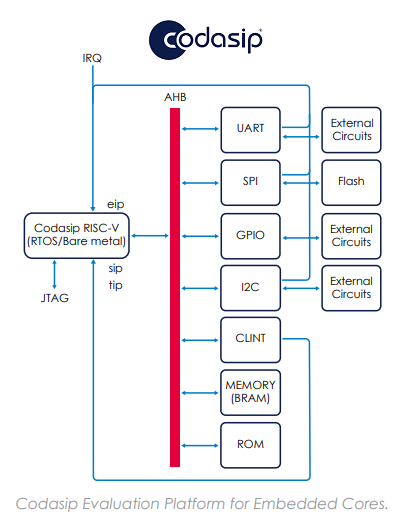

Codasip has created two new FPGA evaluation platforms to test their technology, one for embedded and one for application cores. An example board can be found here for prototyping architectures. These platforms consist of your selected RISC-V processor with a subsystem containing peripherals and AMBA interconnect. A testbench layer includes a clock generator and block RAMs for internal memories and can use some of the FPGA peripherals such as flash memory. Additionally, users receive a Vivado project and bitstream files for their target FPGA board. The platforms include an SDK, software examples, and step-by-step documentation on how to use the peripherals. If known, please select your preferred core from the list below when applying for a board.

The newly introduced A730 application core (not shown) also supports the industry’s first implementation of CHERI (Capability Hardware Enhanced RISC Instructions) memory protection technology, which enables controlled partitioning of memory and software. This security solution breaks the chain of attack by restricting access and permissions of software within a system and prevents attackers from moving beyond the initial point of entry. For more information regarding CHERI, follow the link to the interview below or fill out the application form to get connected with Codasip.

(All images sourced from Codasip)