Published

11 December 2025

Written by Luke Forster

CHERI-Based Microcontrollers for Embedded Security

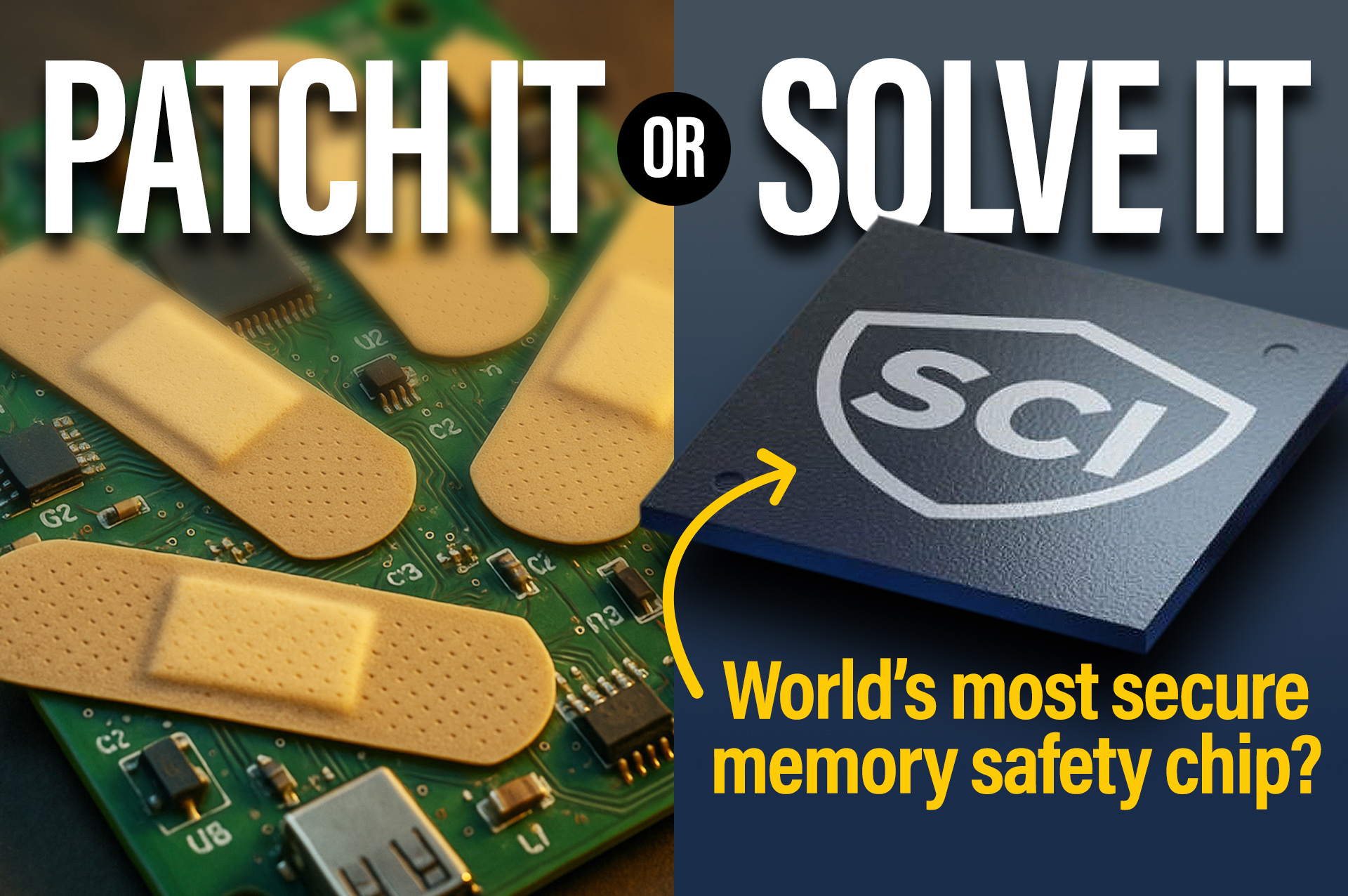

What if your microcontroller could prevent memory corruption by design? SCI Semiconductor is developing CHERI-based secure microcontrollers that build memory safety directly into the silicon. Based on the CHERIoT-Ibex RISC-V core, these chips are built for industrial and embedded environments where traditional software-based security just isn’t enough.

Instead of patching vulnerabilities at the firmware level, SCI’s solution uses capability-based hardware to stop common exploits, like buffer overflows, before they can even happen. This puts CHERI-based secure microcontrollers at the heart of a new wave of secure, resilient embedded systems.

What is CHERI, and why does it matter?

CHERI stands for Capability Hardware Enhanced RISC Instructions. Originally funded by DARPA and developed with the University of Cambridge, it redefines how a processor handles memory access -giving each pointer a set of permissions and bounds that are enforced by the CPU.

SCI’s implementation uses the CHERIoT-Ibex core, which is designed specifically for embedded use. This makes it possible to integrate hardware-level memory safety into microcontrollers used for things like industrial control, medical devices, or automotive systems – without a performance hit.

You still write C or Rust code. But when you compile with a CHERIoT-aware toolchain, the hardware ensures each memory access is valid. No hacks. No extra runtime. No “fingers crossed” approach to safety.

Ideal for critical infrastructure

SCI’s CHERI-based secure microcontrollers are particularly suited to operational technology environments. Think grid controllers, secure access gateways, or robotics. These are places where memory corruption bugs could cause real-world damage – or open up networks to cyberattack.

With CHERI in the silicon, these MCUs can enforce least privilege access between subsystems, ensure that rogue pointers can’t hijack execution, and protect against use-after-free or buffer overflow bugs by default.

The result is a chip that doesn’t just run your code, but verifies the safety of how that code interacts with memory – making it easier to meet certification requirements and protect long-life deployments in the field.

Developer-friendly from day one

One of SCI’s biggest priorities is developer usability. The CHERIoT toolchain supports familiar languages and development flows, and the company is working to make its devices compatible with common RTOS and security stacks.

Evaluation kits are expected to launch in 2026. If you’re working in a domain where security, power efficiency, and deterministic behaviour all matter, these parts might be a strong fit.

A shift in how we think about embedded security

Most engineers are used to thinking about MCU security in terms of software updates, cryptography, or secure boot. CHERI adds another layer – one that prevents entire classes of bugs from happening in the first place. It’s not just about what you can do with the microcontroller. It’s about what you can no longer do—and that’s a good thing.

With adoption from companies like SCI Semiconductor, CHERI may finally move from research into real-world production silicon. If you’re designing products that need to run reliably for years, CHERI-based secure microcontrollers might be the memory-safe foundation you’ve been waiting for.

Comments are closed.

Comments

No comments yet