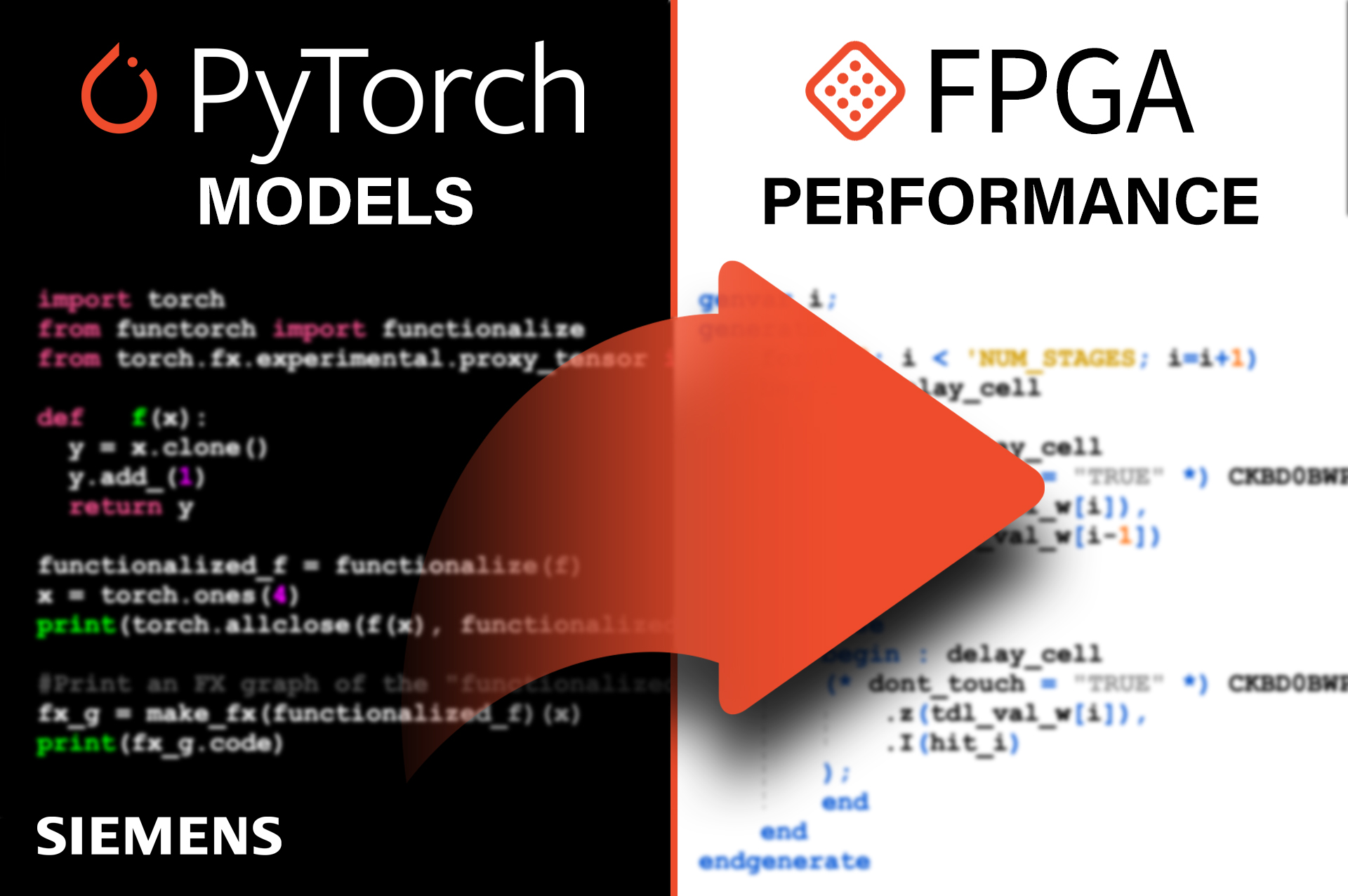

Running ML models on hardware used to mean painful hours writing HDL. But in 2025, tools like Siemens EDA’s Catapult High-Level Synthesis are flipping the script.

Catapult HLS lets you convert Python-trained ML models—built in PyTorch, TensorFlow, or Keras—directly into RTL for FPGAs or ASICs. That’s right: you can go from Python to hardware, skipping the hand-coded Verilog altogether.

Why would anyone want to run ML on an FPGA in the first place? The answer is flexibility and efficiency. MCUs and NPUs work well for many use cases—but when you need tight control over power, performance, or layout, nothing beats custom silicon. FPGAs give you that control, and Catapult gives you a way to design for them without deep hardware expertise.

Instead of writing HDL from scratch, Catapult lets engineers start from high-level code like C++, SystemC, or Python. The tool then generates synthesizable RTL, ready for deployment. This is especially powerful for machine learning models, which can now be trained in popular frameworks and compiled straight to hardware logic.

The benefits are huge. You get to experiment with different architectures, optimise for energy use or speed, and create custom accelerators tailored to your exact ML workload. Whether you’re targeting edge devices, automotive systems, or smart industrial controllers, this gives you full-stack control without the traditional headaches.

It also lowers the barrier to entry. Electrical engineering students who hated their HDL assignments—or software engineers with no hardware background—can now be part of the hardware design process. This expands the talent pool and speeds up development cycles.

Catapult’s support for AI-centric frameworks means you don’t need to change your software workflow to get hardware acceleration. And because it’s part of Siemens EDA’s toolchain, it integrates seamlessly with ASIC and FPGA development flows.

If you’re working on AI at the edge, building embedded ML systems, or just want to stop writing HDL, Siemens EDA’s Catapult HLS is the tool to watch.

Comments are closed.

Comments

No comments yet