Products

Solutions

Published

8 May 2025

Written by Emily Curryer

Codasip came to Embedded World 2025 with a message loud and clear: you don’t need to be a processor guru to build your own RISC-V custom processor acceleration. And you certainly don’t need a room full of verification engineers to do it either.

This is good news for design engineers who want more performance from less silicon—without writing bespoke compiler toolchains or risking software compatibility nightmares.

From Lean Core to Lightning-Fast Execution

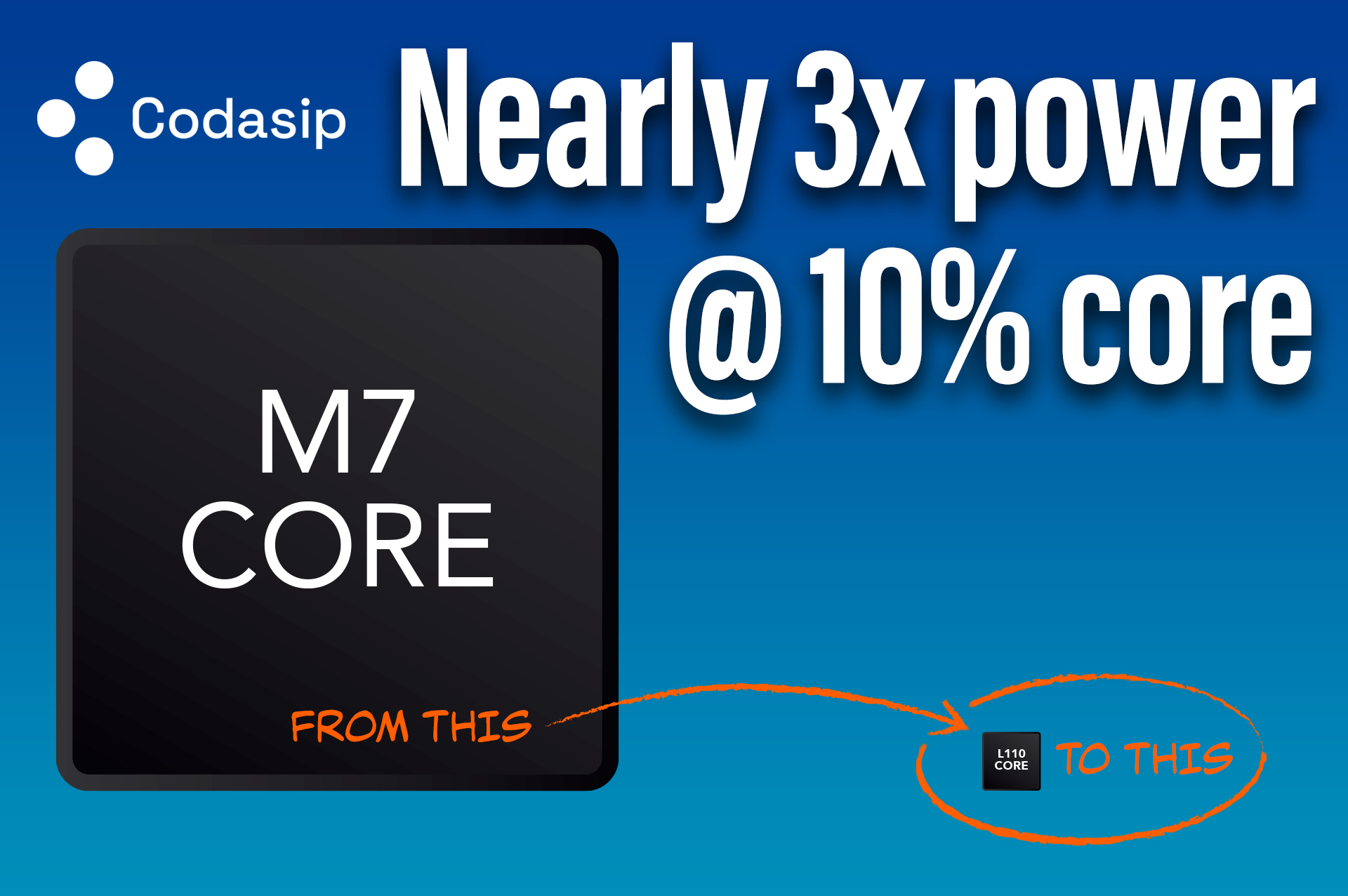

At the heart of Codasip’s offering is the L110 RISC-V core—just 7% the size of a typical ARM Cortex-M7, yet capable of comparable performance. How? It’s all down to smart, bounded customisation.

By adding targeted acceleration to the base core—using off-the-shelf primitives and custom instructions—Codasip demonstrated up to 15x performance gains over the original. Best of all? This acceleration is abstracted from the software engineer. Your code doesn’t change. You just get more bang per clock cycle.

Acceleration That Hides Behind the API

Software teams get to keep their beloved libraries. Whether it’s DSP functions or neural network workloads, Codasip’s approach means the underlying performance boost happens under the hood.

Using standard APIs (like CMSIS-DSP), the enhanced RISC-V core handles custom instructions without requiring a software rewrite. You simply drop in your code, and the magic happens behind the scenes.

No Processor Team? No Problem

Traditionally, only processor vendors or giants with sprawling SoC design teams could attempt this level of customisation. Codasip flips that model.

With Codaspip Studio, even companies without dedicated hardware design or verification teams can start creating accelerators. The base core remains untouched—meaning it stays fully verified—while your tweaks remain safely ring-fenced and easy to test.

This makes RISC-V custom processor acceleration a real option for system integrators and smart sensor developers alike.

Smart Sensors, Smarter Systems

Keith from Codasip highlighted some compelling application areas—smart sensors, for one. Think audio or vibration sensors that can process data locally, detecting anomalies or danger faster, and relaying it sooner to the wider system.

Imagine crash avoidance systems in cars, where milliseconds matter. Now imagine giving those sensors the intelligence to react faster without bloating the silicon or power budget. That’s the kind of real-world edge AI enablement Codasip is offering.

Getting Started with Codasip Studio

Engineers can dive in with Codasip Studio, which comes bundled with base RISC-V IP, example projects, and clear tutorials on building custom instructions. With an arsenal of primitives and training material, Codasip equips you to experiment, iterate, and deploy at your own pace.

To learn more and start your acceleration journey, visit codasip.com.

So next time you need to squeeze maximum performance from minimal resources, remember: RISC-V custom processor acceleration is no longer just for the processor elite. Kodasip just handed you the keys.

Comments are closed.

Comments

No comments yet